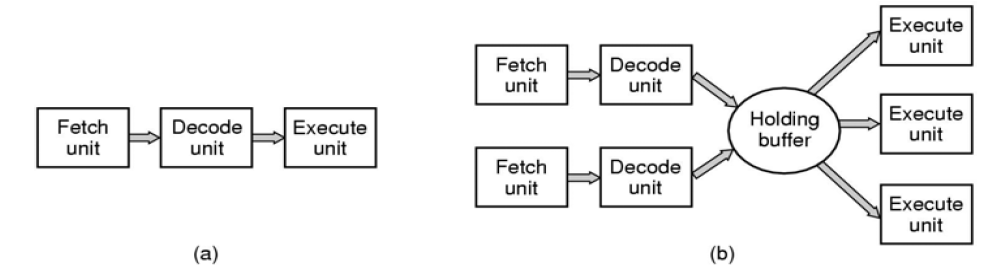

1. Instruction Execution

- While executing a program, the CPU

- fetches the next instruction from memory (loading into IR)

- decodes it to determine its type and operands

- executes it

- May take multiple clock cycles to execute an instruction

- Example:

- LOAD R1, #3

- LOAD R2, M2

- STORE M3, R4

- ADD R1, R2, R3

- Each CPU has a specific set of instructions that it can execute (instruction-set architecture)

2. Registers

- General registers (data/address)

- Program Counter (PC): contains the memory address of the next instruction to be fetched

- Stack Pointer (PC): points to the top of current stack in memory. T

- the stack contains one frame for each procedure that has been entered but not yet exited

- Program Status Word (PSW): contains the condition code bits and various other control bits.

- Note: when time multiplexing the CPU, the operating system will often stop the running program to (re)start another one. In these cases, it must save the "state information" (e.g., value of the registers)

3. Computer-System Operation

8. I/O Structure

- I/O devices and CPU can execute concurrency

- Each device controller has local buffer(s).

- CPU moves data from/to main memory to/from local buffers.

- I/O is from/to device to/from local buffer of controller

- The device driver is special operating software that interacts with the device controller

- Typically, the device controller informs CPU that it has finished its operation by causing an interrupt.

4. Instruction Cycle with Interrupts

5. Classes of Interrupts

- I/O interrupts: generated by an I/O controller, to signal normal completion of an operation or to signal a variety of error conditions

- Timer Interrupts: generated by a timer within the processor. This allows the operating system to perform certain functions on a regular basis.

- Hardware Failure Interrupts: generated by a failure (e.g., power failure or memory parity error).

- Traps (Software Interrupts): generated by some condition that occurs as a result of an instruction execution

- error

- user request for an operating system service

6. Interruption Mechanism

- Interrupt transfers control to the interrupt service routine generally through the interrupt vector (e.g., Interl) which contains the addresses of all the service routines. (Alternatively, the machine has a status register or cause register that holds the reason for the interrupt - MIPS architecture)

- Interrupt Service Routines (ISRs): separate segments of code determine what action should be taken for each type of interrupt

- Once the interrupt has been serviced by the ISR, the control is returned to the interrupted program. Need to save the "process state" (register, PC, ...) before ISR takes over.

7. Basic Interrupt Processing

- the interrupt is issued

- processor finishes execution of current instruction

- processor signals acknowledgement of interrupt

- processor pushes PSW and PC onto control stack

- processor loads new PC value through the interrupt vector

- ISR saves remainder of the process state information

- ISR executes

- ISR restores process state information

- Old PSW and PC values are restored from the control stack

8. I/O Structure

- After I/O starts, control returns to user program only upon I/O completion

- wait instruction idles the CPU until the next interrupt

- wait loop (contention for memory access)

- at most one I/O request is outstanding at a time, no simultaneous I/O processing

- After I/O starts, control returns to user program without waiting for I/O completion

- system call: request to the operating system to allow user to wait for I/O completion

- device-status table contains entry for each I/O device indicating its type address, and state

- operating system indexes into I/O devices table to determine device status and to modify table entry to include interrupt

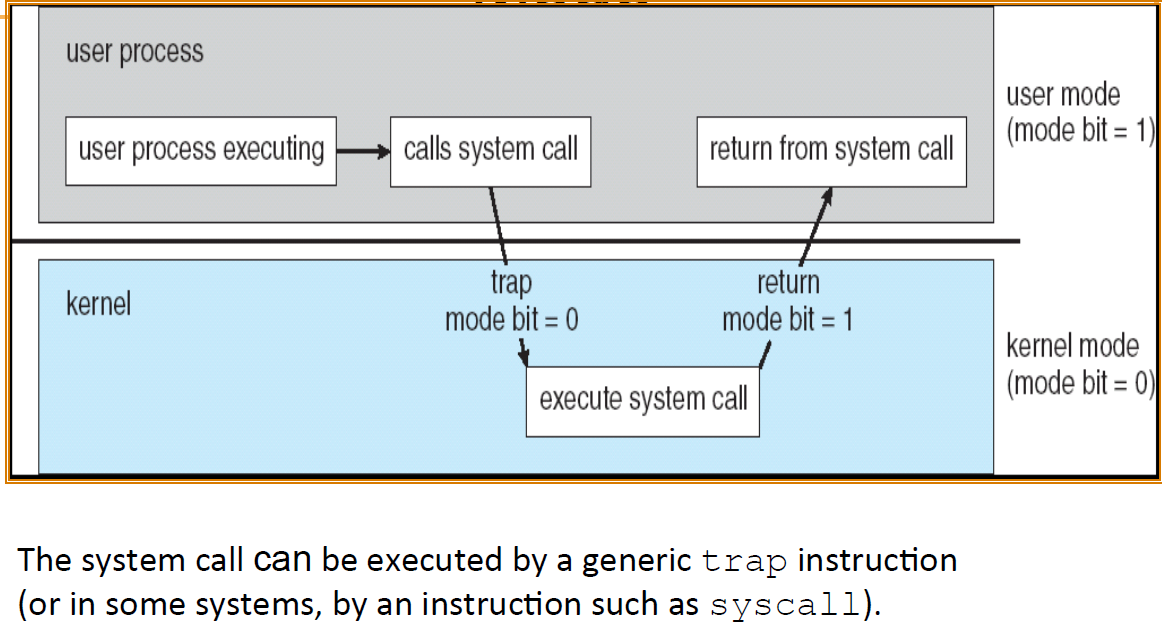

9. Dual-Mode Operation

- Operating system must protect itself and all other programs (and their data) from any malfunctioning program

- Provide hardware support to differentiate between at least two modes of operations

- user mode: execution done on behalf of a user

- kernel mode: (also monitor mode or system mode): execution done on behalf of operating system.

- Mode bit added to computer hardware to indicate the current mode

- kernel: 0

- user: 1

- When an interrupt occurs hardware switches to kernel mode

- Privileged instructions can be issued only in kernel mode

10. Transition form user to kernel mode

No comments:

Post a Comment